Abstract

Comparison Multi-core Processor The embedded multiprocessor center has become a standard approach in scientific and engineering applications. Field-Programmable Gate Arrays (FPGAs) enable the implementation of complex logic systems on a single programmable device. However, embedded multiprocessors face challenges related to thread safety.

The structured processor architecture includes on-chip transmitter and receiver modules, along with processing and control units. These components work together to transmit and receive data on a single die. The system completes data transfers using fewer instructions compared to general-purpose processors.

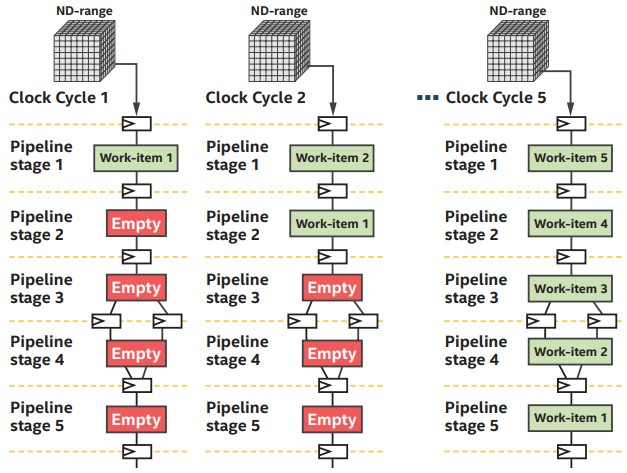

The multi-core processor interface allows designers to create coprocessors with advanced control capabilities. These include handling data-dependent I/O, saving and restoring task states during context switches, and enabling pipelined processing. This paper demonstrates how this interface supports the development of reusable and cost-efficient coprocessors.

Comparison of Multi-Core Processors

The rise of new media applications—such as time-shift recording, 3D gaming, video conferencing, and interactive MPEG-4—demands increased flexibility in consumer electronic products. Additionally, the variation in required application sets across products, countries, and evolving standards calls for a strategic design approach.

To manage complexity, reduce design costs, and shorten time-to-market, developers must adopt a versatile media-processing platform suitable for a wide range of resource-constrained products. For instance, an Eclipse DCT coprocessor can time-share both forward and inverse DCT functions required for simultaneous MPEG-2 encoding and decoding in time-shift recording systems.Comparison Multi-core Processor

Currently, several vendors are entering the market with platforms that partially meet these requirements [1],[2]. These coprocessors handle multitasking efficiently and can time-share workloads across various applications. As a result, application complexity no longer depends solely on the number of coprocessors in the system.

This multiprocessor center design is completely designed in the wake of actualizing

towards the inserted simultaneous processor.

For example, a medium-grain task such as the Discrete Cosine Transform (DCT) is essential for MPEG encoding and decoding.